EUROPEAN SOUTHERN OBSERVATORY Organisation Européenne pour des Recherches Astronomiques dans l'Hémisphère Austral Europäische Organisation für astronomische Forschung in der südlichen Hemisphäre

## **VERY LARGE TELESCOPE**

## **New General Detector Controller (NGC)**

## **USER MANUAL**

Doc.-No. VLT-MAN-ESO-13660-4510

Issue 1 Date 18/01/2008 90 pages

| Prepared: | M.Meyer    |      |           |  |  |  |

|-----------|------------|------|-----------|--|--|--|

|           | Name       | Date | Signature |  |  |  |

| Approved: | D.Baade    |      |           |  |  |  |

|           | Name       | Date | Signature |  |  |  |

| Released: | A.Moorwood |      |           |  |  |  |

|           | Name       | Date | Signature |  |  |  |

|     |                                 | Doc:   | VLT-TRE-ESO-13660-3900 |

|-----|---------------------------------|--------|------------------------|

| ESO | ESO General Detector Controller | Issue: | 1.1                    |

|     | (NGC)                           | Date:  | 08/03/2006             |

|     |                                 | Page:  | 2 of 90                |

|     | USER MANUAL                     |        |                        |

## **CHANGE RECORD**

| Issue | Date       | Affected Paragraphs(s) | Reason/Initiation/Remarks |

|-------|------------|------------------------|---------------------------|

| 1     | 05/02/2008 | All                    | First version             |

|       |            |                        |                           |

|       |            |                        |                           |

|       |            |                        |                           |

|       |            |                        |                           |

|     |                                 | Doc:   | VLT-TRE-ESO-13660-3900 |

|-----|---------------------------------|--------|------------------------|

| ESO | ESO General Detector Controller | Issue: | 1.1                    |

|     | (NGC)                           | Date:  | 08/03/2006             |

|     |                                 | Page:  | 3 of 90                |

|     | USER MANUAL                     |        |                        |

## **TABLE OF CONTENTS**

| PURPOSE                                                                                                                                 | 5  |

|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| Reference Documents                                                                                                                     |    |

| Links                                                                                                                                   | 5  |

| List of Abbreviations/Acronyms                                                                                                          |    |

| 1 INTRODUCTION                                                                                                                          |    |

| 2 OVERVIEW                                                                                                                              |    |

|                                                                                                                                         |    |

| 2.1 Block                                                                                                                               |    |

| 2.2 Minimum DFE System – Basic Board with Backplane and Transition                                                                      |    |

| Board                                                                                                                                   |    |

| 3 FUNCTIONAL DESCRIPTION                                                                                                                | 10 |

| 3.1 High Speed Links                                                                                                                    | 10 |

| 3.2 Link Transmission and Function Addressing                                                                                           | 11 |

| 3.3 Back-End                                                                                                                            | 13 |

| 3.4 Front-End                                                                                                                           | 21 |

| 3.4.1 Front-End-Basic Board (FEB)                                                                                                       |    |

| 3.4.1.1 Configuration Register                                                                                                          | 25 |

| 3.4.1.2 Status and ID Register                                                                                                          |    |

| 3.4.1.3 Monitor                                                                                                                         |    |

| 3.4.1.4 Detector Bias Generation<br>3.4.1.5 Telemetry                                                                                   |    |

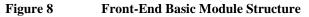

| 3.4.1.6 Sequencer                                                                                                                       |    |

| 3.4.1.6.1 Principle                                                                                                                     |    |

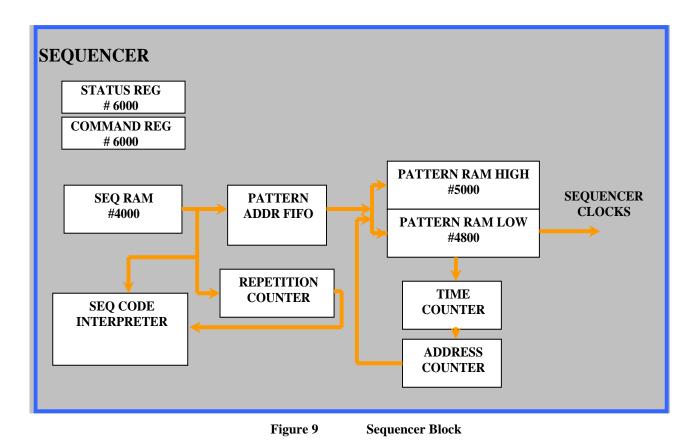

| 3.4.1.7 NGC Trigger and Shutter Control                                                                                                 |    |

| <ul><li>3.4.1.7.1 NGC Trigger – IR Operation</li><li>3.4.1.7.2 NGC Trigger – Shutter Operation</li></ul>                                |    |

| 3.4.1.8 AQ Manager                                                                                                                      |    |

| 3.4.1.9 Basic Board Front Panel                                                                                                         |    |

| 3.4.1.10 Video Chain                                                                                                                    |    |

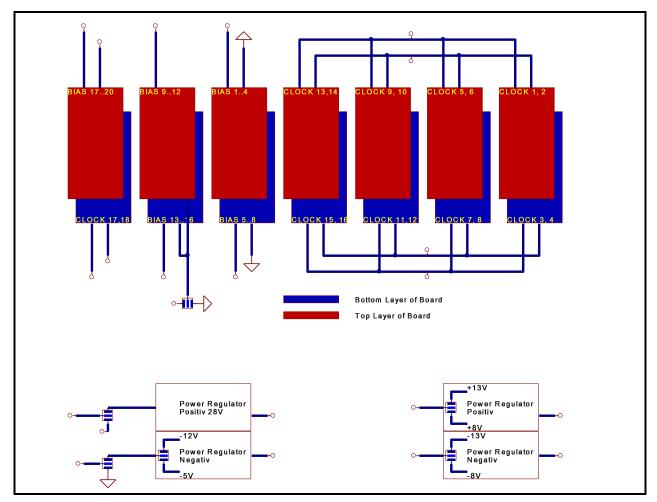

| 3.4.1.11 Clock and Bias Rails and Settings                                                                                              |    |

| 3.4.1.12 Basic Board Jumpers                                                                                                            |    |

| 3.4.2 Transition Board of Front-End Basic-Board<br>3.4.2.1 Flexible Read-out of Multi-output CCDs with Switches on the Transition Board |    |

| 3.4.2.1 Flexible Read-out of Multi-output CCDs with Switches on the Transition Board<br>3.4.3 AO32 Board                                |    |

| 3.4.3 AQ32 Dould<br>3.4.3.1 Configuration Register                                                                                      |    |

| 3.4.3.2 Status Register                                                                                                                 |    |

| 3.4.3.3 Monitor                                                                                                                         |    |

|     |                                        | Doc:   | VLT-TRE-ESO-13660-3900 |

|-----|----------------------------------------|--------|------------------------|

| ESO | <b>ESO General Detector Controller</b> | Issue: | 1.1                    |

| 200 | (NGC)                                  | Date:  | 08/03/2006             |

|     | USER MANUAL                            | Page:  | 4 of 90                |

| 3.4.3.4  | Conversion Error Register        | 76 |

|----------|----------------------------------|----|

| 3.4.3.5  | Sequencer                        |    |

| 3.4.3.6  | Video Offset Register            | 77 |

| 3.4.3.7  | AQ Manager                       | 77 |

| 3.4.4 Tr | ansition Board of the AQ32 Board | 79 |

| 3.5 NGC  | Front-End Backplane              |    |

| 3.6 PM   | C Based Low Latency DMA Channel  |    |

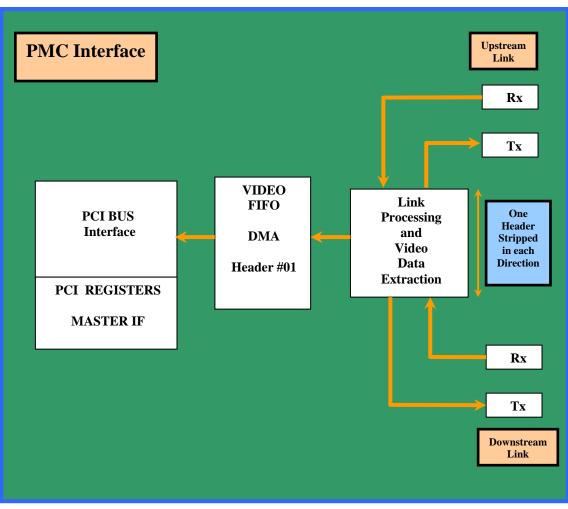

| 3.6.1 P  | MC Interface                     |    |

|     |                                 | Doc:   | VLT-TRE-ESO-13660-3900 |

|-----|---------------------------------|--------|------------------------|

| ESO | ESO General Detector Controller | Issue: | 1.1                    |

|     | (NGC)                           | Date:  | 08/03/2006             |

|     |                                 | Page:  | 5 of 90                |

|     | USER MANUAL                     |        |                        |

## PURPOSE

This document describes operation of the New General Detector Controller REV1 hardware. It gives an understanding of the basic operation, tells about the implemented firmware and is also intended as a programmers guide for software evaluation.

## **Reference Documents**

| NGC Infrared Detector Control Software – User Manual | Jörg Stegmeier  |

|------------------------------------------------------|-----------------|

| Document Number: VLT-MAN-ESO-13660-4085              |                 |

| NGC Optical DCS - User Manual                        | Andrea Balestra |

| Document Number: VLT-MAN-ESO-13660-4086              | Claudio Cumani  |

| NGC Base Software - Design Description               | Jörg Stegmeier  |

| Doc.No. VLT-SPE-ESO-13660-3836                       |                 |

| Next Generation detector Controller Requirements     | D. Baade        |

| ESO-Doc. No. VLT-SPE-ESO-13660-3207                  |                 |

#### Links

| FPGA          | http://www.xilinx.com |

|---------------|-----------------------|

| ADC, DAC      | http://www.analog.com |

| Printed Board | http://www.andus.de   |

|               |                       |

## List of Abbreviations/Acronyms

| ADCAnalog to Digital ConverterAQData AcquisitionDACDigital to Analog ConverterDFEDetector Front-End ElectronicsDBEDetector Back-End ElectronicsDMADirect Memory AccessFPGAField Programmable Gate ArrayFIFOFirst in First out MemoryIRACEInfrared Array Control ElectronicsNGCNew General ControllerRTCReal-time ComputerRxLink ReceiverTxLink Transmitter |       |                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------|

| DACDigital to Analog ConverterDFEDetector Front-End ElectronicsDBEDetector Back-End ElectronicsDMADirect Memory AccessFPGAField Programmable Gate ArrayFIFOFirst in First out MemoryIRACEInfrared Array Control ElectronicsIRQInterrupt requestNGCNew General ControllerRTCReal-time ComputerRxLink ReceiverRxTxLink Transceiver                           | ADC   | Analog to Digital Converter        |

| DFEDetector Front-End ElectronicsDBEDetector Back-End ElectronicsDMADirect Memory AccessFPGAField Programmable Gate ArrayFIFOFirst in First out MemoryIRACEInfrared Array Control ElectronicsIRQInterrupt requestNGCNew General ControllerRTCReal-time ComputerRxLink ReceiverRxTxLink Transceiver                                                         | AQ    | Data Acquisition                   |

| DBEDetector Back-End ElectronicsDMADirect Memory AccessFPGAField Programmable Gate ArrayFIFOFirst in First out MemoryIRACEInfrared Array Control ElectronicsIRQInterrupt requestNGCNew General ControllerRTCReal-time ComputerRxLink ReceiverRxTxLink Transceiver                                                                                          | DAC   | Digital to Analog Converter        |

| DMADirect Memory AccessFPGAField Programmable Gate ArrayFIFOFirst in First out MemoryIRACEInfrared Array Control ElectronicsIRQInterrupt requestNGCNew General ControllerRTCReal-time ComputerRxLink ReceiverRxTxLink Transceiver                                                                                                                          | DFE   | Detector Front-End Electronics     |

| FPGAField Programmable Gate ArrayFIFOFirst in First out MemoryIRACEInfrared Array Control ElectronicsIRQInterrupt requestNGCNew General ControllerRTCReal-time ComputerRxLink ReceiverRxTxLink Transceiver                                                                                                                                                 | DBE   | Detector Back-End Electronics      |

| FIFOFirst in First out MemoryIRACEInfrared Array Control ElectronicsIRQInterrupt requestNGCNew General ControllerRTCReal-time ComputerRxLink ReceiverRxTxLink Transceiver                                                                                                                                                                                  | DMA   | Direct Memory Access               |

| IRACEInfrared Array Control ElectronicsIRQInterrupt requestNGCNew General ControllerRTCReal-time ComputerRxLink ReceiverRxTxLink Transceiver                                                                                                                                                                                                               | FPGA  | Field Programmable Gate Array      |

| IRQInterrupt requestNGCNew General ControllerRTCReal-time ComputerRxLink ReceiverRxTxLink Transceiver                                                                                                                                                                                                                                                      | FIFO  | First in First out Memory          |

| NGCNew General ControllerRTCReal-time ComputerRxLink ReceiverRxTxLink Transceiver                                                                                                                                                                                                                                                                          | IRACE | Infrared Array Control Electronics |

| RTCReal-time ComputerRxLink ReceiverRxTxLink Transceiver                                                                                                                                                                                                                                                                                                   | IRQ   | Interrupt request                  |

| RxLink ReceiverRxTxLink Transceiver                                                                                                                                                                                                                                                                                                                        | NGC   | New General Controller             |

| RxTx     Link Transceiver                                                                                                                                                                                                                                                                                                                                  | RTC   | Real-time Computer                 |

|                                                                                                                                                                                                                                                                                                                                                            | Rx    | Link Receiver                      |

| Tx Link Transmitter                                                                                                                                                                                                                                                                                                                                        | RxTx  | Link Transceiver                   |

|                                                                                                                                                                                                                                                                                                                                                            | Тх    | Link Transmitter                   |

|     |                                 | Doc:   | V. |

|-----|---------------------------------|--------|----|

| ESO | ESO General Detector Controller | Issue: |    |

|     | (NGC)                           | Date:  |    |

|     |                                 | Page:  |    |

|     | USER MANUAL                     | _      |    |

## **1 INTRODUCTION**

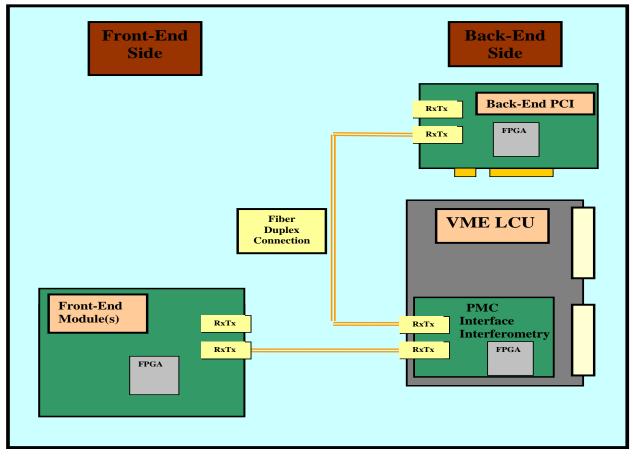

NGC is a modular system consisting of the Back-End module with PCI based connection to the data acquisition computer and the Front-End module(s), generating and receiving detector signals. Data and control signals between Back-End and Front-End modules are on fiber-optic link(s) with transmission rates of 2.5 GBit/s. The modularity of the system allows many combinations as multiple Back-Ends or multiple Front-Ends or combinations as desired.

Emphasis is given to low power dissipation, what is mainly important for the Front-End unit to allow operation without cooling units. The Basic Board, a complete four channel system on one board of standard VME 6U size, consumes less than 10 Watts. The AQ32 board with 32 video channels on a board of the same size has ~15 Watts of power consumption.

No processor on the Front-End side is implemented. The data acquisition computer can address all Front-End functions over the fiber link. Result is a quiet system without difficult to control processor bus activity during data acquisition.

There is no parallel video or communication data bus on the Front-End. All data and communication transfer runs over high speed serial links with transmission rates of 2.5 GBit/s. Result is minimum disturbance for the anticipated low noise operation on the low level detector signals.

All voltages for clocks and biases of the detector are remotely programmable also during readout of the detector to allow maximum comfort for evaluation and test.

Digital galvanic isolated outputs for shutter, wobbling mirror and markers are provided and the system can accept a trigger input for synchronizing the detector read-out to external events.

Monitors for video and clocks are on front-panel connectors for evaluation and maintenance.

All detector bias voltages and currents can be measured with the implemented telemetry system.

A minimum number of different components are used, glue logic is not needed due to the fact that all digital logic is implemented in high density VIRTEX-I I Pro FPGAs. All this makes maintenance easy and reliability high.

## **2 OVERVIEW**

## 2.1 Block

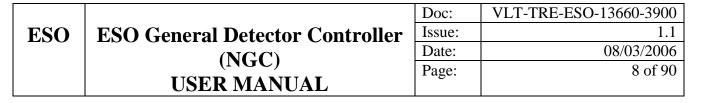

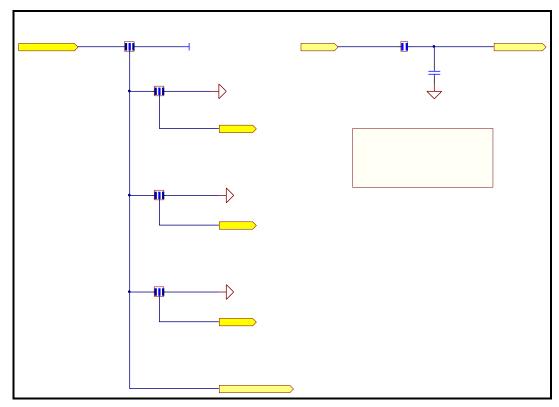

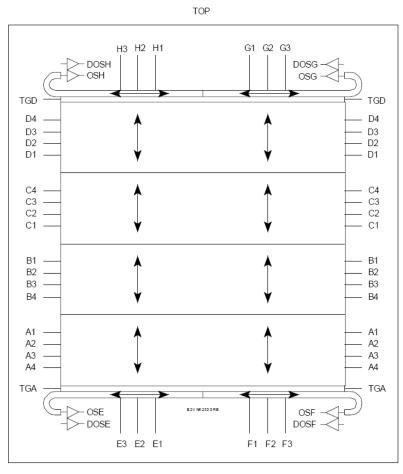

There are two main groups of modules (Figure 1) connected by fiber duplex connection :

- The Detector Back-End Electronics.

- The Detector Front-End Electronics consists of the Basic Module(s) and if needed additional AQ modules. These are interconnected by high speed copper serial links on the backplane for command and data transfer.

The basic link configuration is the linear connection of modules. Commands are routed always from the Back-End to the first Detector Front-End Electronics module. Additional DFE modules are addressed by wormhole routing from previous modules. The same happens for answers or video data from DFE modules to DBE modules.

If more bandwidth is needed two links in parallel can be used (needs different IP on FPGA). Additional functionality can be provided if frames of video data are routed directly out of AQ modules to additional receivers, e.g. PCI based DBE's.

Figure 1 System Block

|     |                                 | Doc:   | VLT-TRE-ESO-13660-3900 |

|-----|---------------------------------|--------|------------------------|

| ESO | ESO General Detector Controller | Issue: | 1.1                    |

|     | (NGC)                           | Date:  | 08/03/2006             |

|     |                                 | Page:  | 9 of 90                |

|     | USER MANUAL                     |        |                        |

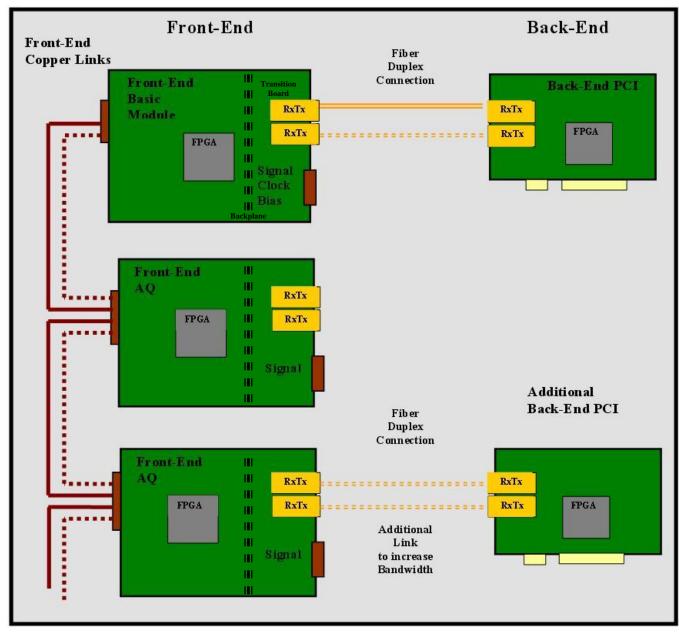

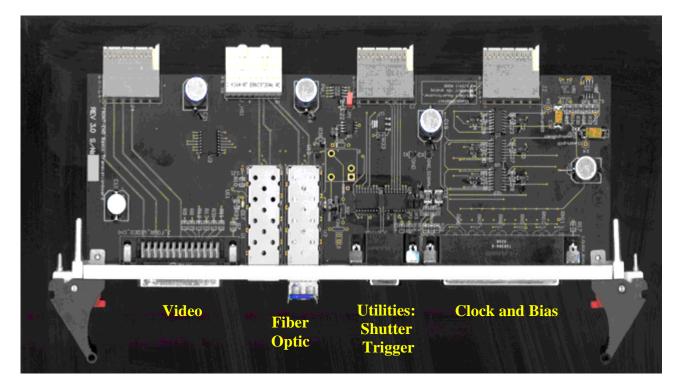

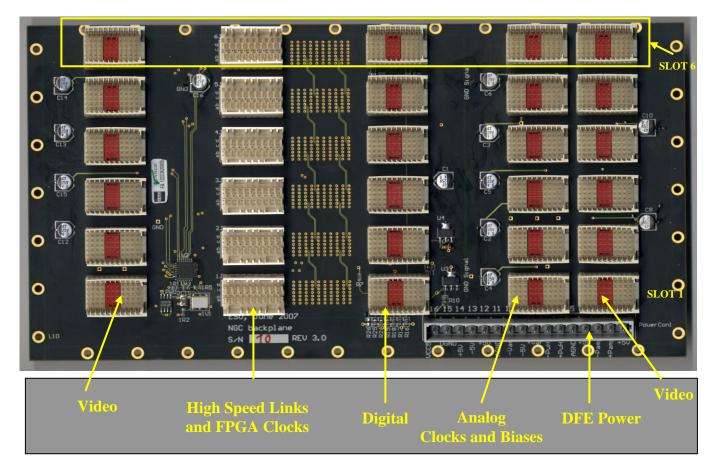

## 2.2 Minimum DFE System – Basic Board with Backplane and Transition Board

A complete DFE consists of the main board(s), the backplane and the Transition Board(s) (Figure 2). The backplane establishes the inter board module connections.

The Transition Board sets up the connection to external functions like clocks, biases, video inputs and fiber links. In addition the Transition Board can hold special functionality not implemented in the main board.

Figure 2 Minimum NGC System with Basic Board, Backplane and Transition Board

## **3 FUNCTIONAL DESCRIPTION**

## 3.1 High Speed Links

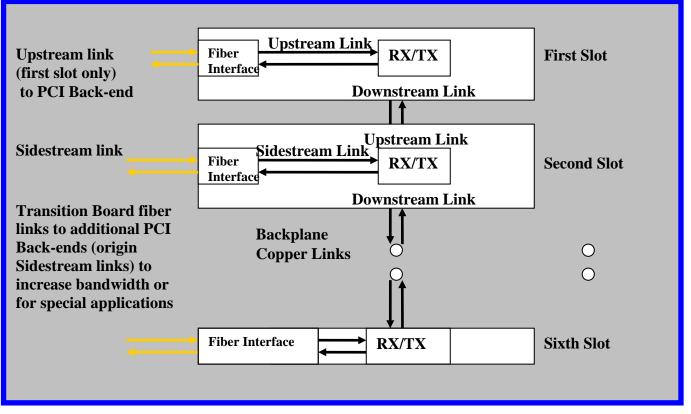

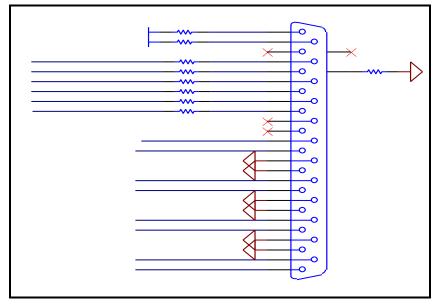

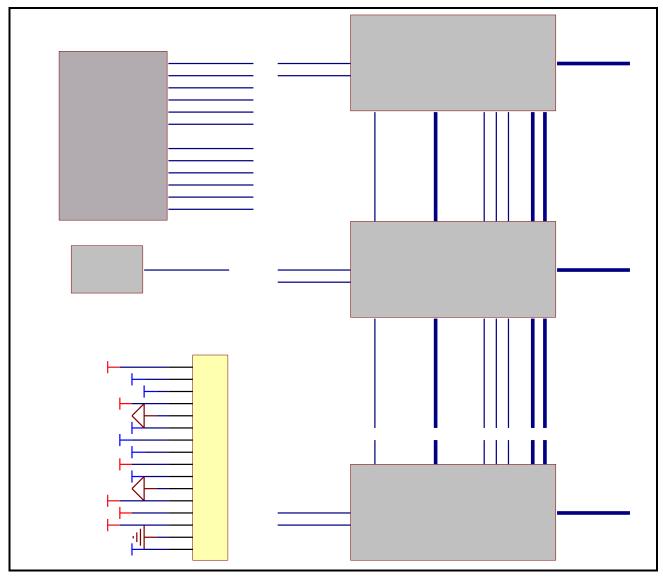

Data transfer and communication work purely on serial links. The bandwidth of one link is ~200MB/s and scales well with 33MHz PCI 64. The link architecture is determined by the connections on the backplane (Figure 3 and Figure 38), the use of the Transition Board back panel fiber optic links and the firmware in the FPGA.

**Terminology** : Upstream link is a link in direction towards the Back-end, Downstream link is a link in direction away from the Back-end. Sidestream link is the link to the fiber interface of the Transition Board.

On slot 1 the upstream link is routed by backplane connection always to the fiber interface on the Transition board. The Downstream link connects over the backplane to the Upstream link of the next board in the chain. Succeeding boards connect serially to each other over the backplane. More bandwidth and computing power will be available, when on a board the Upstream link is closed, the Sidestream link is opened and the Sidestream link is routed out of the Fiber interface on the Transition Board to an additional PCI interface. This PCI interface has then full control on the chain downstream (see also 3.5.1 Front-End Configuration Register).

Figure 3 High Speed Links

|     |                                 | Doc:   | VLT-TRE-ESO-13660-3900 |

|-----|---------------------------------|--------|------------------------|

| ESO | ESO General Detector Controller | Issue: | 1.1                    |

|     | (NGC)                           | Date:  | 08/03/2006             |

|     | ~ /                             | Page:  | 11 of 90               |

|     | USER MANUAL                     |        |                        |

## 3.2 Link Transmission and Function Addressing

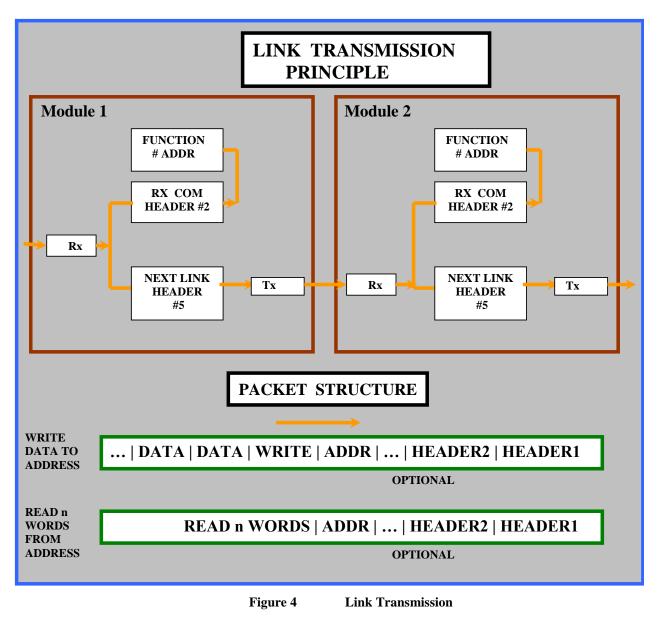

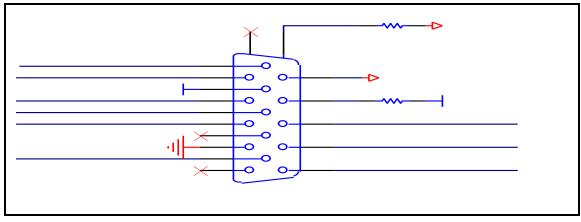

The communication between all system modules is based on packet transmission over serial links. The principle of communication is the same for all modules (Figure 4). A packet structure is defined to address a function (e.g. a register or memory in a front-end module) for read or write. Upstream of module1 is the Back-End module. If from there a write to a function in module1 has to be executed, the packet header (#2) addresses first RX COM, then the address of the function (#ADDR). The next word determines that a WRITE has to be executed. The data to write are in the next word (DATA).

|     |                                 | Doc:   | VLT-TRE-ESO-13660-3900 |

|-----|---------------------------------|--------|------------------------|

| ESO | ESO General Detector Controller | Issue: | 1.1                    |

|     | (NGC)                           | Date:  | 08/03/2006             |

|     | × ,                             | Page:  | 12 of 90               |

|     | USER MANUAL                     |        |                        |

If more data statements follow, RX COM automatically increments #ADDR, and the writes are guided to consecutive locations.

A write to #ADDR in module2 has as first word the header for NEXT LINK (#5), the next word addresses RX COM (#2), next word is WRITE, then the DATA words follow. Any word in the packet is 32 Bits wide.

## Example

Write data word content (Sequencer start = 1) to Sequencer Command register #6000 in module1 : Packet must be filled with : #2 #6000 #0 #1

If the sequencer would be in module2 on downstream link : Packet must be filled with : #5 #2 #6000 #0 #1

Reading data from a module has a similar structure. The function is addressed as before only the WRITE (#0) has to be replaced with a READ (#80000000) and then the number of words to read (#Number of Words). The read words are then automatically transmitted back to the receiver module (RX COM) in the Back-End.

#### Example

Read 10 words from sequencer memory in module1 (Sequencer RAM #4000): Packet must be filled with : #2 #4000 #80000000 #A

If the sequencer would be in module2 on downstream1 link : Packet must be filled with : #5 #2 #4000 #80000000 #A

|     |                                 | Doc:   | VLT-TRE-ESO-13660-3900 |

|-----|---------------------------------|--------|------------------------|

| ESO | ESO General Detector Controller | Issue: | 1.1                    |

|     | (NGC)                           | Date:  | 08/03/2006             |

|     |                                 | Page:  | 13 of 90               |

|     | USER MANUAL                     |        |                        |

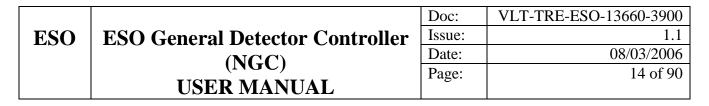

## 3.3 Back-End

- Back-End PCI is a module with connection to a 64 Bit PCI bus.

- Function is based on the XILINX Virtex Pro FPGA XC2VP7 FF 672 .

- A PCI master/slave interface with scatter/gather DMA is implemented.

- The slave IF is used for communication.

- The master IF is used for video data DMA transfers to PCI.

- RocketIO transceivers (2.5 GBit each) are used for communication and data transfers

Figure 5 PCI Back-End

Figure 6 Back-End Structure

The Back-End module (Figure 5 and Figure 6) connects to the data acquisition computer via a 64 bit PCI bus interface based on a XILINX IP core. The PCI bus interface has master and slave capabilities. The slave forms the communication interface to the Front-End, the master is responsible for DMA transfers of the Front-End video data to the acquisition computers memory. Commands and data transfers can run concurrently. The communication between Back-End and any Front-End module is based on packet transmission over high speed serial links. Data packets for communication have to be written to TX COM, read data packets from the Rx link are routed into RX COM. The COMMAND REGISTER initiates actions like fifo clear or transmission start. The STATUS REGISTER holds status information like fifo status or the transfer acknowledge bit. Video data from the link are automatically routed to the VIDEO FIFO.

A transfer handshake protocol must always be followed for communication operations.

- The packet has to be written from PCI to the Back-End transmitter fifo (address #10).

- Then the transmission has to be initiated by writing from PCI to the command register (Write h10 to address #14).

- Then the Acknowledge register ( address #14) has to be polled till acknowledge is received ( Bit 7 set ).

|     |                                 | Doc:   | VLT-TRE-ESO-13660-3900 |

|-----|---------------------------------|--------|------------------------|

| ESO | ESO General Detector Controller | Issue: | 1.1                    |

|     | (NGC)                           | Date:  | 08/03/2006             |

|     |                                 | Page:  | 15 of 90               |

|     | USER MANUAL                     |        |                        |

- Acknowledge register Bit 0 declares a finished operation, Bit 1 successful operation on a valid address.

- Acknowledge register is cleared by reading the receiver fifo (address #10)

## **Addresses**

Table 1 Configuration Space

| Relative<br>address[Hex] | Function                       |

|--------------------------|--------------------------------|

| Config Space             |                                |

| C W                      | DMA Control Register           |

| 10 R/W                   | Read Rx FiFo / Write Tx Fifo   |

| 14 R                     | COMmunication Status Register  |

| 1C W                     | COMmunication Command Register |

| 68 R/W                   | PCI_Descr_Pointer #90 ADI      |

| 84 R/W                   | PCI_Addr_Reg                   |

| 8C R/W                   | PCI_DMA_Counter_Reg            |

| 90 R/W                   | PCI_Descr_Pointer              |

| A0 R                     | PCI_Board Revision and Date    |

Hint : Read from NGC Panel with "ior local 0x<rel addr>"

Table 2DMA Space

| Relative     | Function            |

|--------------|---------------------|

| address[Hex] |                     |

| DMA Space    |                     |

| 0            |                     |

| 8 R          | DMA Status Register |

## **Registers**

Table 3 DMA Status Register – Read

(Addr #8)

| Bit 5 | Data FiFo Empty        |

|-------|------------------------|

| Bit 6 | Data FiFo Full         |

| Bit 7 | Data FiFo Full – Write |

|       | (Cleared by Clr Data   |

|       | FiFo)                  |

Table 4 Read Rx FiFo / Write Tx FiFo

( Addr #10 )

#### Table 5 Communication Command – Write (Addr #1C)

| BIT 0 | Clear Com FiFos    |

|-------|--------------------|

| Bit 1 | Clear Video FiFo   |

| Bit 4 | Transfer Enable TX |

| Bit 7 | Test Box Enable    |

## ESO General Detector Controller (NGC) USER MANUAL

| Doc:   | VLT-TRE-ESO-13660-3900 |

|--------|------------------------|

| Issue: | 1.1                    |

| Date:  | 08/03/2006             |

| Page:  | 17 of 90               |

| _      |                        |

Table 6 Communication Status – Read

(Addr #14)

| BIT 0  | Ack Received                       |

|--------|------------------------------------|

| Bit 1  | Valid Address accessed             |

| Bit 5  | Video FiFo Empty                   |

| BIT 6  | Video FiFo Full                    |

| Bit 7  | <b>Overflow Error Flag</b>         |

|        | (Write on Video FiFo Full -        |

|        | <b>Cleared by Clr Video FiFo</b> ) |

| Bit 8  | RX FIFO Empty                      |

| Bit 9  | RX FIFO Full                       |

| Bit 10 | TX FIFO Empty                      |

| Bit 11 | TX FIFO Full                       |

| Bit 12 | Link Channel Up                    |

| Bit 13 | Link Hard Error                    |

| Bit 14 | Link Soft Error                    |

| Bit 15 | Link Framing Error                 |

Table 7

Interrupt\_Ctr\_Reg

( Addr #68 )

Bit 21 Interrupt Flag

Table 8 PCI\_Addr\_Reg (Addr #84)

Bit 0..31 DMA Address

Table 9 PCI\_DMA\_Counter

( Addr #8C )

Bit 2..12 DMA Count

Table 10 PCI\_Descr\_Pointer (Addr #90)

Bit 4..31 Initial DMA Descriptor

Table 11 PCI Backend Board ID Register (Addr #A0)

PCI Backend HW Revision 2 Firmware Revision 1.1 )

|                                  | Volue 1 - Degio Deservi             |

|----------------------------------|-------------------------------------|

|                                  | Value = 1 $\rightarrow$ Basic Board |

| Bit (30) Board Type              | $2 \rightarrow AQ32$                |

|                                  | 8 → PCI Backend                     |

|                                  | 0                                   |

|                                  | 0                                   |

|                                  | 0                                   |

| _                                | 1                                   |

|                                  | Value = 1 33MHz Latency disabled    |

| Bit (74) Board Sub-type          |                                     |

| Bit 4                            | 1                                   |

| Bit 5                            | 0                                   |

| Bit 6                            | 0                                   |

| Bit 7                            | 0                                   |

|                                  |                                     |

| Bit (118) HW Revision            |                                     |

|                                  | 0                                   |

| Bit 9                            | 1                                   |

| Bit 10                           | 0                                   |

| Bit 11                           | 0                                   |

|                                  |                                     |

| Bit (1512) Firmware Revision     |                                     |

| Bit 12                           | 1                                   |

| Bit 13                           | 0                                   |

| Bit 14                           | 0                                   |

| Bit 15                           | 0                                   |

|                                  |                                     |

| Bit (1916) Firmware Sub-Revision |                                     |

| Bit 16                           | 1                                   |

| Bit 17                           | 0                                   |

| Bit 18                           | 0                                   |

| Bit 19                           | 0                                   |

|                                  |                                     |

|                                  |                                     |

|                                  |                                     |

Table 12 DMA Command Register – Write only (Addr #A8)

| BIT 1 | Start DMA       |

|-------|-----------------|

| Bit 2 | Abort DMA       |

| Bit 3 | Clear Interrupt |

|     |                                 | Doc:   | VLT-TRE-ESO-13660-3900 |

|-----|---------------------------------|--------|------------------------|

| ESO | ESO General Detector Controller | Issue: | 1.1                    |

|     | (NGC)                           | Date:  | 08/03/2006             |

|     |                                 | Page:  | 21 of 90               |

|     | USER MANUAL                     |        |                        |

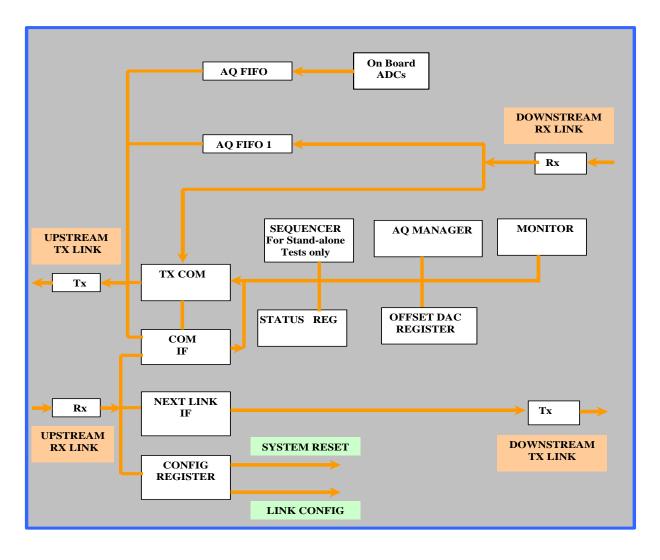

## 3.4 Front-End

The Front-End is connected to the Back-End with an Upstream link. A Downstream link on the first Front-End module connects to a downstream module like AQ32 or other basic modules (more clocks and biases or multiple detectors). From there again a link connects downstream to the next module.

Before any addressing of functions on Front-End modules the link structure of the Front-End system must be defined. This happens by writing to the CONFIG register of each module.

RX\_COM together with TX\_COM form the communication interface on the Front-End. The upstream link send all set-up and command information for the onboard functions to RX\_COM, where address and data are extracted and send to the individual on board modules - replies from the addressed modules enter TX\_COM for uplink transmission.

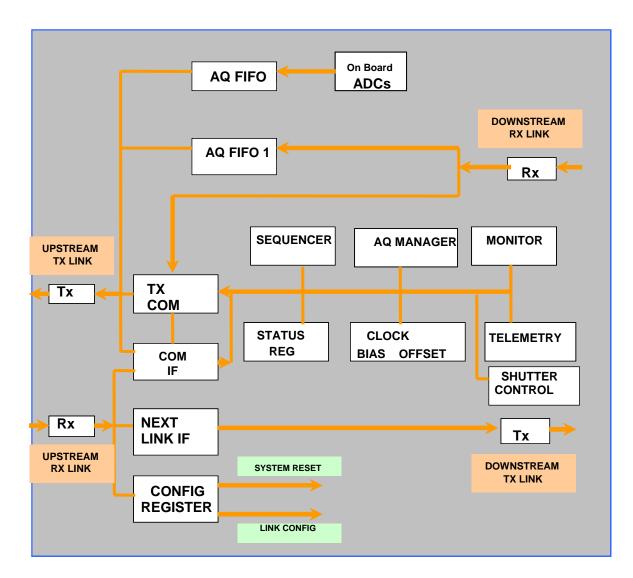

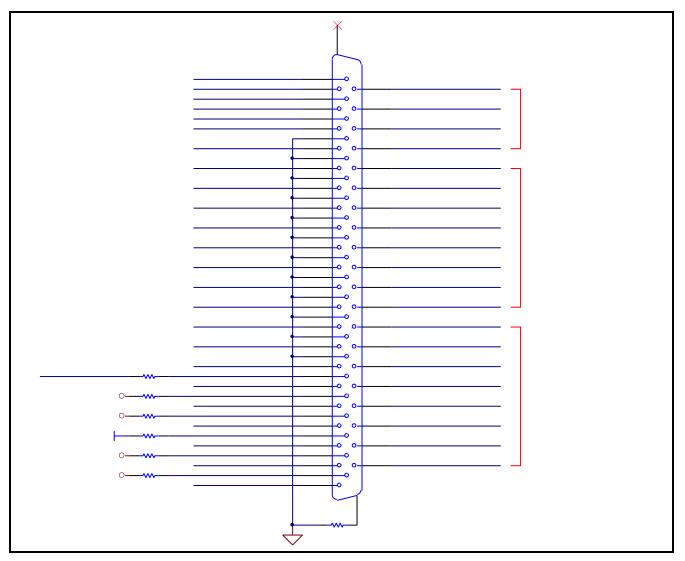

The module structure is the same for all Front-End modules (FEB shown in Figure 8, AQ32 in Figure 34), only the set of registers differs slightly between FEB and AQ32.

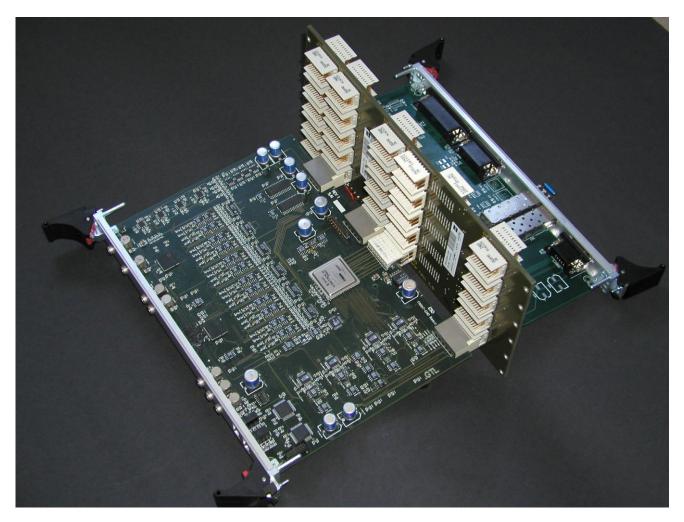

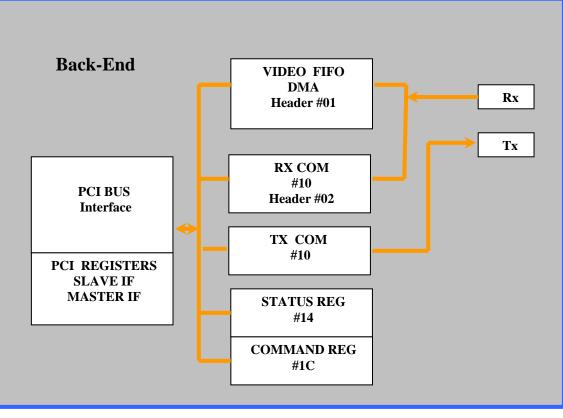

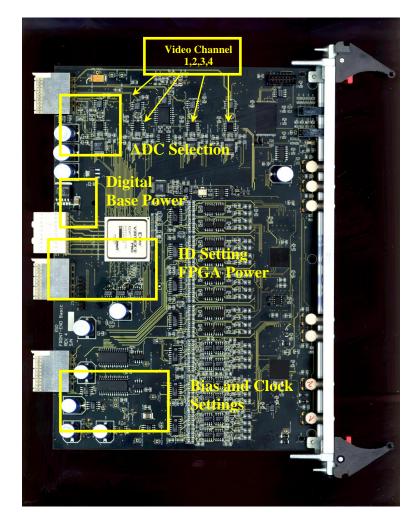

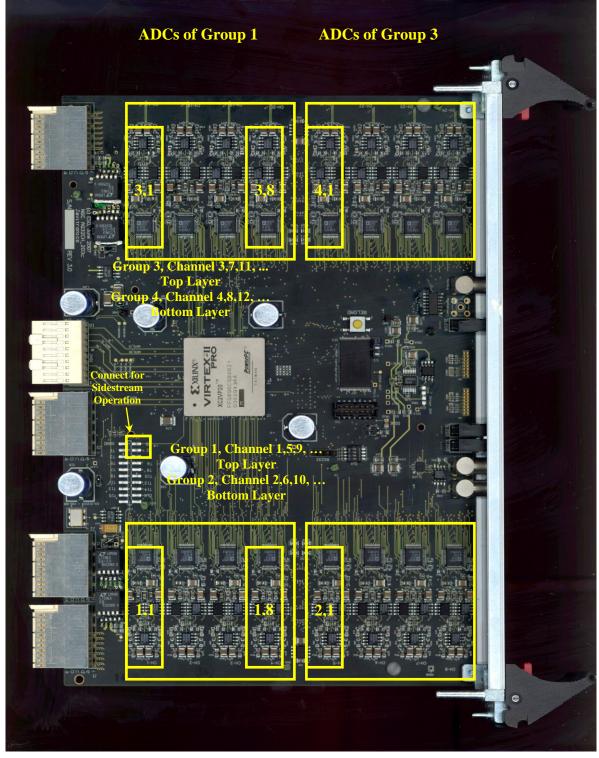

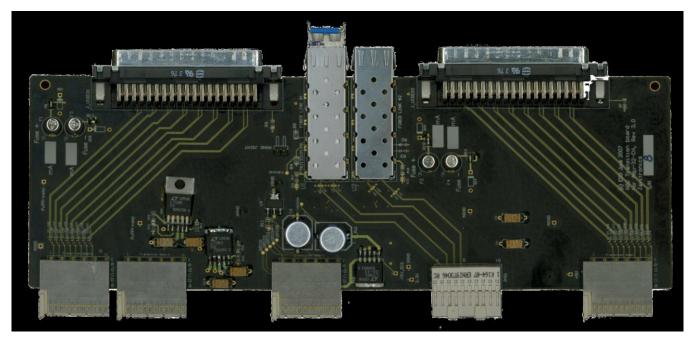

## 3.4.1 Front-End-Basic Board (FEB)

The Front-End Basic Module (Figure 7) is based on the XILINX Virtex Pro FPGA XC2VP7 FF 672. Main functions of this module are

- Communication

- Video data transfer

- Sequencer

- DAC voltage generator for clock and bias

- Clock drivers (18 clocks)

- Bias drivers (18 biases)

- Four data acquisition channels ( can be installed with either 16 or 18 Bit ADC's )

- Telemetry

- Clock monitoring

- Video monitoring

- Communication and data transfer to the Back-End is handled with the FPGA's RocketI/O transceivers.

- The sequencer is completely contained within the FPGA. The digital clock driver lines of the sequencer connect without glue logic to the clock driver switches.

- The ADC outputs of the four acquisition channels connect without glue logic to the FPGA due to the high pin count available there. Used ADC's are the AD76xx types from Analog Devices. The preamplifier input is fully differential (see Table 39 on next page).

- Connection to additional multi channel AQ modules is over the backplane by copper with the high speed links of the FPGA.

- Telemetry of biases and clocks.

- > Two independent Monitors for clocks.

- Monitor for video signals.

# ESOESO General Detector Controller<br/>(NGC)Doc:VLT-TRE-ESO-13660-3900Issue:1.1Date:08/03/2006Page:23 of 90

Figure 7 Front-End Basic Module

|     |                                 | Doc:   | VLT-TRE-ESO-13660-3900 |

|-----|---------------------------------|--------|------------------------|

| ESO | ESO General Detector Controller | Issue: | 1.1                    |

|     | (NGC)                           | Date:  | 08/03/2006             |

|     |                                 | Page:  | 24 of 90               |

|     | USER MANUAL                     |        |                        |

The module structure of the Front-End-Basic Board is shown below (Figure 8 Front-End Basic Module Structure). The corresponding module blocks are described in the following sections.

## 3.4.1.1 Configuration Register

Each NGC Front-End board has a Configuration Register. Before any addressing of functions on Front-End modules the link structure of the Front-End system must be defined. This is accomplished in the Front-End Link Config Register(s) [Bit 3..0]. It is the only register on the Front-End where no handshake signals are generated, just because without structure definition no reply is possible. These registers (for each board) are the first ones to set in any system set-up. The registers are addressed directly by header addressing in an order that the modules next to the Back-End have to be programmed first.

A general module reset [Bit 15] similar to power up can also be executed by this register.

Remark on link direction : Uplink on a NGC Front-End board has the direction from module towards Back\_End, Downlink direction correspondingly away from Back\_End.

#### Table 13 Configuration Register (Header 0X8)

| BIT 30         | Number of UpStream links till   |

|----------------|---------------------------------|

| <b>B</b> 11 50 | -                               |

|                | Back-End (Minimum is 1)         |

| BIT 54         | Not used                        |

| BIT 6          | SidelinkNotUplink               |

|                | Closes the Uplink and switches  |

|                | to the Sidelink on the          |

|                | <b>Transition Board for</b>     |

|                | communication and data          |

|                | transfer (1)                    |

| BIT 7          | Downlink_Powerdown              |

|                | Unpowers the Downlink of this   |

|                | module                          |

| BIT 148        | Not used                        |

| Bit 15         | <b>Global Reset</b> (pulsed)    |

|                | Resets module to power up       |

|                | condition and puts global reset |

|                | to backplane what resets all    |

|                | boards connected to the         |

|                | backplane.                      |

|                | (Not affected are sequencer     |

|                | memories and bias/clock         |

|                | voltage settings)               |

|     |                                 | Doc:   | VLT-TRE-ESO-13660-3900 |

|-----|---------------------------------|--------|------------------------|

| ESO | ESO General Detector Controller | Issue: | 1.1                    |

|     | (NGC)                           | Date:  | 08/03/2006             |

|     |                                 | Page:  | 26 of 90               |

|     | USER MANUAL                     |        |                        |

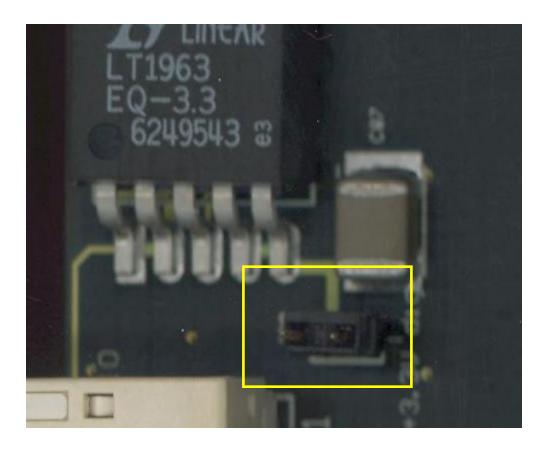

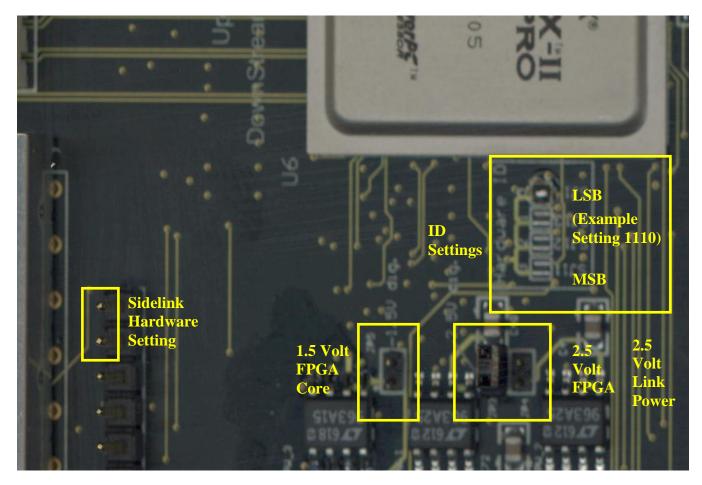

(1) The sidelink option can also be set by a hardware jumper( see Figure 22). When the jumper is set, BIT 6 of the configuration register is a "don't care".

## Example :

Module1 (e.g. Basic Module) connected to Back-End = 1 upstream link on Module1 Module2 ( e.g. first AQ32 ) connected to Basic module = 2 upstream links for Module2 Module3 ( e.g. second AQ32 ) connected to Module2 = 3 upstream links for Module3 Module4 (e.g. second Basic Module) connected Module3 = 4 upstream links for Module4

Packet Data for the Front-End Configuration Register :

| 0X8 0x1             | (Basic module)        |

|---------------------|-----------------------|

| 0x5 0x8 0x2         | (first AQ32 module )  |

| 0x5 0x5 0x8 0x3     | (second AQ32 module ) |

| 0x5 0x5 0x5 0x8 0x4 | (second Basic module) |

## 3.4.1.2 Status and ID Register

Front-End status contains two read only registers. The status register contains the module status information. The ID register describs module set-up.

Table 14 Status Register – Read only

ADDR #1000

| BIT 0UPSTREAM_CHANNEL_UPBit 1SIDESTREAM_CHANNEL_UPBit 2DOWNSTREAM1_CHANNEL_UPBIT 3UPSTREAM_HARD_ERRORBit 4SIDESTREAM_HARD_ERRORBit 5DOWNSTREAM1_HARD_ERRORBit 6UPSTREAM_SOFT_ERRORBit 7SIDESTREAM_SOFT_ERRORBit 8DOWNSTREAM1_SOFT_ERRORBit 9UPSTREAM_FRAME_ERRORBit 10SIDESTREAM_FRAME_ERRORBit 11DOWNSTREAM1_FRAME_ERRORBit 12Not usedBit 13Not usedBit 14Not usedBit 15Not usedBit 16Not usedBit 17Not usedBit 18Not usedBit 19Not usedBit 20RX_COM_FIFO_EMPTYBit 21RX_COM_FIFO_FULLBit 22TX_AQ_FIFO1_FULLBit 23TX_AQ_FIFO1_FULLBit 24TX_COM_FIFO_FULLBit 25TX_AQ_FIFO2_FULLBit 26TX_COM_FIFO_FULLBit 27TX_COM_FIFO_FULLBit 29NEXT_LINK_FIFO_EMPTYBit 20NEXT_LINK_FIFO_EMPTYBit 23NEXT_LINK_FIFO_EMPTYBit 24NEXT_LINK_FIFO_EMPTYBit 25NEXT_LINK_FIFO_EMPTYBit 30OUTPUT ENABLEDBit 30OUTPUT ENABLEDBit 31SEQUENCER RUNNING |               |                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------|

| Bit 2DOWNSTREAM1_CHANNEL_UPBIT 3UPSTREAM_HARD_ERRORBit 4SIDESTREAM_HARD_ERRORBit 5DOWNSTREAM1_HARD_ERRORBit 6UPSTREAM_SOFT_ERRORBit 7SIDESTREAM_SOFT_ERRORBit 7SIDESTREAM_SOFT_ERRORBit 9UPSTREAM_FRAME_ERRORBit 10SIDESTREAM_FRAME_ERRORBit 11DOWNSTREAM1_FRAME_ERRORBit 12Not usedBit 13Not usedBit 14Not usedBit 15Not usedBit 16Not usedBit 17Not usedBit 18Not usedBit 20RX_COM_FIFO_EMPTYBit 21RX_COM_FIFO_FULLBit 22TX_AQ_FIFO1_EMPTYBit 23TX_AQ_FIFO1_FULLBit 24TX_AQ_FIFO2_FULLBit 25TX_AQ_FIFO_FULLBit 26RX_COM_FIFO_FULLBit 27TX_COM_FIFO_FULLBit 29NEXT_LINK_FIFO_FULLBit 29NEXT_LINK_FIFO_EMPTYBit 30OUTPUT ENABLED                                                                                                                                                                                            | BIT 0         | UPSTREAM_CHANNEL_UP      |

| BIT 3UPSTREAM_HARD_ERRORBit 4SIDESTREAM_HARD_ERRORBit 5DOWNSTREAM1_HARD_ERRORBit 6UPSTREAM_SOFT_ERRORBit 7SIDESTREAM_SOFT_ERRORBit 7SIDESTREAM_SOFT_ERRORBit 9UPSTREAM_FRAME_ERRORBit 10SIDESTREAM_FRAME_ERRORBit 11DOWNSTREAM1_FRAME_ERRORBit 12Not usedBit 13Not usedBit 14Not usedBit 15Not usedBit 16Not usedBit 17Not usedBit 18Not usedBit 20RX_COM_FIFO_EMPTYBit 21RX_COM_FIFO_FULLBit 22TX_AQ_FIFO1_EMPTYBit 23TX_AQ_FIFO1_FULLBit 24TX_AQ_FIFO2_FULLBit 25TX_AQ_FIFO2_FULLBit 26TX_COM_FIFO_FULLBit 27TX_COM_FIFO_FULLBit 29NEXT_LINK_FIFO_FULLBit 29NEXT_LINK_FIFO_EMPTYBit 30OUTPUT ENABLED                                                                                                                                                                                                                      | Bit 1         | SIDESTREAM_CHANNEL_UP    |

| Bit4SIDESTREAM_HARD_ERRORBit5DOWNSTREAM1_HARD_ERRORBit6UPSTREAM_SOFT_ERRORBit7SIDESTREAM_SOFT_ERRORBit7SIDESTREAM_SOFT_ERRORBit9UPSTREAM_FRAME_ERRORBit10SIDESTREAM_FRAME_ERRORBit11DOWNSTREAM1_FRAME_ERRORBit11DOWNSTREAM1_FRAME_ERRORBit12Not usedBit13Not usedBit14Not usedBit15Not usedBit16Not usedBit17Not usedBit18Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO1_FULLBit24TX_AQ_FIFO2_FULLBit25TX_AQ_FIFO2_FULLBit26TX_COM_FIFO_FULLBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                    | Bit 2         | DOWNSTREAM1_CHANNEL_UP   |

| Bit5DOWNSTREAM1_HARD_ERRORBit6UPSTREAM_SOFT_ERRORBit7SIDESTREAM_SOFT_ERRORBit8DOWNSTREAM1_SOFT_ERRORBit9UPSTREAM_FRAME_ERRORBit10SIDESTREAM_FRAME_ERRORBit11DOWNSTREAM1_FRAME_ERRORBit11DOWNSTREAM1_FRAME_ERRORBit12Not usedBit13Not usedBit14Not usedBit15Not usedBit16Not usedBit17Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit23TX_AQ_FIFO1_EMPTYBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO2_FULLBit26TX_COM_FIFO_FULLBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                              | BIT 3         | UPSTREAM_HARD_ERROR      |

| Bit6UPSTREAM_SOFT_ERRORBit7SIDESTREAM_SOFT_ERRORBit8DOWNSTREAM1_SOFT_ERRORBit9UPSTREAM_FRAME_ERRORBit10SIDESTREAM_FRAME_ERRORBit11DOWNSTREAM1_FRAME_ERRORBit12Not usedBit12Not usedBit13Not usedBit14Not usedBit15Not usedBit16Not usedBit17Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO1_FULLBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO_FULLBit26TX_COM_FIFO_FULLBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                   | Bit 4         | SIDESTREAM _HARD_ERROR   |

| Bit7SIDESTREAM_SOFT_ERRORBit8DOWNSTREAM1_SOFT_ERRORBit9UPSTREAM_FRAME_ERRORBit10SIDESTREAM_FRAME_ERRORBit11DOWNSTREAM1_FRAME_ERRORBit11DOWNSTREAM1_FRAME_ERRORBit12Not usedBit13Not usedBit14Not usedBit15Not usedBit16Not usedBit17Not usedBit18Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO1_FULLBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO1_FULLBit26TX_COM_FIFO_FULLBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                          | Bit 5         | DOWNSTREAM1_HARD_ERROR   |

| Bit8DOWNSTREAM1_SOFT_ERRORBit9UPSTREAM_FRAME_ERRORBit10SIDESTREAM_FRAME_ERRORBit11DOWNSTREAM1_FRAME_ERRORBit11DOWNSTREAM1_FRAME_ERRORBit12Not usedBit13Not usedBit14Not usedBit15Not usedBit16Not usedBit17Not usedBit18Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit23TX_AQ_FIFO1_EMPTYBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO2_FULLBit26TX_COM_FIFO_FULLBit27TX_COM_FIFO_FULLBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                      | Bit 6         | UPSTREAM_SOFT_ERROR      |

| Bit9UPSTREAM_FRAME_ERRORBit10SIDESTREAM_FRAME_ERRORBit11DOWNSTREAM1_FRAME_ERRORBit11DOWNSTREAM1_FRAME_ERRORBit12Not usedBit13Not usedBit14Not usedBit15Not usedBit16Not usedBit17Not usedBit17Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO1_EMPTYBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO1_FULLBit26TX_COM_FIFO_FULLBit27TX_COM_FIFO_EMPTYBit28NEXT_LINK_FIFO_EMPTYBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                        | Bit 7         | SIDESTREAM _SOFT_ERROR   |

| Bit10SIDESTREAM_FRAME_ERRORBit11DOWNSTREAM1_FRAME_ERRORBit11DOWNSTREAM1_FRAME_ERRORBit12Not usedBit13Not usedBit14Not usedBit15Not usedBit16Not usedBit17Not usedBit18Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO1_FULLBit24TX_AQ_FIFO2_FULLBit25TX_AQ_FIFO2_FULLBit26TX_COM_FIFO_FULLBit27TX_COM_FIFO_FULLBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                   | Bit 8         | DOWNSTREAM1_SOFT_ERROR   |

| Bit11DOWNSTREAM1_FRAME_ERRORBit12Not usedBit12Not usedBit13Not usedBit14Not usedBit15Not usedBit16Not usedBit16Not usedBit17Not usedBit18Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO1_FULLBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO1_FULLBit26TX_COM_FIFO_FULLBit27TX_COM_FIFO_FULLBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                | Bit 9         | UPSTREAM_FRAME_ERROR     |

| Bit12Not usedBit13Not usedBit14Not usedBit15Not usedBit16Not usedBit17Not usedBit17Not usedBit18Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO1_EMPTYBit24TX_AQ_FIFO2_EMPTYBit25TX_AQ_FIFO2_FULLBit26TX_COM_FIFO_FULLBit27TX_COM_FIFO_EMPTYBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>Bit</b> 10 | SIDESTREAM _ FRAME_ERROR |

| Bit13Not usedBit14Not usedBit15Not usedBit16Not usedBit17Not usedBit18Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO1_EMPTYBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO2_FULLBit26TX_COM_FIFO_FULLBit27TX_COM_FIFO_FULLBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 11        | DOWNSTREAM1_FRAME_ERROR  |

| Bit14Not usedBit15Not usedBit16Not usedBit17Not usedBit18Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO1_EMPTYBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO1_FULLBit26TX_COM_FIFO_FULLBit27TX_COM_FIFO_FULLBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 12        | Not used                 |

| Bit15Not usedBit16Not usedBit17Not usedBit18Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO2_EMPTYBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO2_FULLBit26TX_COM_FIFO_FULLBit27TX_COM_FIFO_EMPTYBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit 13        | Not used                 |

| Bit16Not usedBit17Not usedBit18Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO_FULLBit23TX_AQ_FIFO1_EMPTYBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO2_FULLBit26TX_COM_FIFO_FULLBit27TX_COM_FIFO_FULLBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit 14        | Not used                 |

| Bit17Not usedBit18Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO2_EMPTYBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO2_FULLBit26TX_COM_FIFO_FULLBit27TX_COM_FIFO_EMPTYBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit 15        | Not used                 |

| Bit18Not usedBit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO2_EMPTYBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO2_FULLBit26TX_COM_FIFO_FULLBit27TX_COM_FIFO_EMPTYBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 16        | Not used                 |

| Bit19Not usedBit20RX_COM_FIFO_EMPTYBit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO2_EMPTYBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO2_FULLBit26TX_COM_FIFO_FULLBit27TX_COM_FIFO_FULLBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bit 17        | Not used                 |

| Bit 20RX_COM_FIFO_EMPTYBit 21RX_COM_FIFO_FULLBit 22TX_AQ_FIFO1_EMPTYBit 23TX_AQ_FIFO2_EMPTYBit 24TX_AQ_FIFO1_FULLBit 25TX_AQ_FIFO2_FULLBit 26TX_COM_FIFO_FULLBit 27TX_COM_FIFO_EMPTYBit 28NEXT_LINK_FIFO_FULLBit 29NEXT_LINK_FIFO_EMPTYBit 30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bit 18        | Not used                 |

| Bit21RX_COM_FIFO_FULLBit22TX_AQ_FIFO1_EMPTYBit23TX_AQ_FIFO2_EMPTYBit24TX_AQ_FIFO1_FULLBit25TX_AQ_FIFO2_FULLBit26TX_COM_FIFO_FULLBit27TX_COM_FIFO_EMPTYBit28NEXT_LINK_FIFO_FULLBit29NEXT_LINK_FIFO_EMPTYBit30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 19        | Not used                 |

| Bit 22TX_AQ_FIFO1_EMPTYBit 23TX_AQ_FIFO1_EMPTYBit 24TX_AQ_FIFO2_EMPTYBit 25TX_AQ_FIFO2_FULLBit 26TX_COM_FIFO_FULLBit 27TX_COM_FIFO_EMPTYBit 28NEXT_LINK_FIFO_FULLBit 29NEXT_LINK_FIFO_EMPTYBit 30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit 20        | RX_COM_FIFO_EMPTY        |

| Bit 23TX_AQ_FIFO2_EMPTYBit 24TX_AQ_FIFO1_FULLBit 25TX_AQ_FIFO2_FULLBit 26TX_COM_FIFO_FULLBit 27TX_COM_FIFO_EMPTYBit 28NEXT_LINK_FIFO_FULLBit 29NEXT_LINK_FIFO_EMPTYBit 30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit 21        | <b>RX_COM_FIFO_FULL</b>  |

| Bit 24TX_AQ_FIFO1_FULLBit 25TX_AQ_FIFO2_FULLBit 26TX_COM_FIFO_FULLBit 27TX_COM_FIFO_EMPTYBit 28NEXT_LINK_FIFO_FULLBit 29NEXT_LINK_FIFO_EMPTYBit 30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Bit 22        | TX_AQ_FIFO1_EMPTY        |

| Bit 25TX_AQ_FIFO2_FULLBit 26TX_COM_FIFO_FULLBit 27TX_COM_FIFO_EMPTYBit 28NEXT_LINK_FIFO_FULLBit 29NEXT_LINK_FIFO_EMPTYBit 30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit 23        | TX_AQ_FIFO2_EMPTY        |

| Bit 26TX_COM_FIFO_FULLBit 27TX_COM_FIFO_EMPTYBit 28NEXT_LINK_FIFO_FULLBit 29NEXT_LINK_FIFO_EMPTYBit 30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>Bit</b> 24 | TX_AQ_FIFO1_FULL         |

| Bit 27TX_COM_FIFO_EMPTYBit 28NEXT_LINK_FIFO_FULLBit 29NEXT_LINK_FIFO_EMPTYBit 30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>Bit</b> 25 |                          |

| Bit 28NEXT_LINK_FIFO_FULLBit 29NEXT_LINK_FIFO_EMPTYBit 30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>Bit</b> 26 | TX_COM_FIFO_FULL         |

| Bit 29NEXT_LINK_FIFO_EMPTYBit 30OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>Bit</b> 27 | TX_COM_FIFO_EMPTY        |

| Bit 30 OUTPUT ENABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Bit 28</b> | NEXT_LINK_FIFO_FULL      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit 29        | NEXT_LINK_FIFO_EMPTY     |

| Bit 31 SEQUENCER RUNNING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>Bit 30</b> | OUTPUT ENABLED           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit 31        | SEQUENCER RUNNING        |

## ESO General Detector Controller (NGC) USER MANUAL

| Doc:   | VLT-TRE-ESO-13660-3900 |

|--------|------------------------|

| Issue: | 1.1                    |

| Date:  | 08/03/2006             |

| Page:  | 28 of 90               |

|        |                        |

Table 15 ID Register – Read only

ADDR #1002 (Below example Basic Board :

18Bit ADC HW Revision 3 Firmware Revision 4.1)

|                                  | Value = $1 \rightarrow$ Basic Board                                     |

|----------------------------------|-------------------------------------------------------------------------|

| Bit ( 3 0) Board Type            | $2 \rightarrow AQ32$                                                    |

| Dit ( 5 0) Doard Type            |                                                                         |

| BIT 0                            | 1                                                                       |

| Bit 1                            | 0                                                                       |

| Bit 2                            | 0                                                                       |

| BIT 3                            | 0                                                                       |

|                                  | Value = 1 to 4 → 16Bit ADC /1MHz Type 14                                |

| Bit (74) Board Sub-type          | 5 to 8 → 16Bit ADC /1MHz Type 14                                        |

| Dit (7 4) Doard Sub-type         | 9 to 12 → 16Bit ADC /3MHz Type 14<br>13 to 15 → 18Bit ADC /1MHz Type 14 |

| Bit 4                            | Set by external Jumpers                                                 |

| Bit 5                            | Set by external Jumpers                                                 |

| Bit 6                            | Set by external Jumpers                                                 |

| Bit 7                            | Set by external Jumpers                                                 |

|                                  | Set by external sumpers                                                 |

|                                  |                                                                         |

| Bit (11 8) HW Revision           |                                                                         |

| Bit 8                            | 1                                                                       |

| Bit 9                            | 1                                                                       |

| Bit 10                           | 0                                                                       |

| Bit 11                           | 0                                                                       |

|                                  |                                                                         |

| Bit (1512) Firmware Revision     |                                                                         |

| Bit 12                           | 0                                                                       |

| Bit 13                           | 0                                                                       |

| Bit 14                           | 1                                                                       |

| Bit 15                           | 0                                                                       |

|                                  |                                                                         |

| Bit (1916) Firmware Sub-Revision |                                                                         |

| Bit 16                           | 1                                                                       |

| Bit 17                           | 0                                                                       |

| Bit 18                           | 0                                                                       |

| Bit 19                           | 0                                                                       |

|                                  | v<br>                                                                   |

|                                  |                                                                         |

| Bit 31 20                        | reserved                                                                |

|                                  |                                                                         |

# ESOESO General Detector Controller<br/>(NGC)Doc:VLT-TRE-ESO-13660-3900Issue:1.1Date:08/03/2006Page:29 of 90

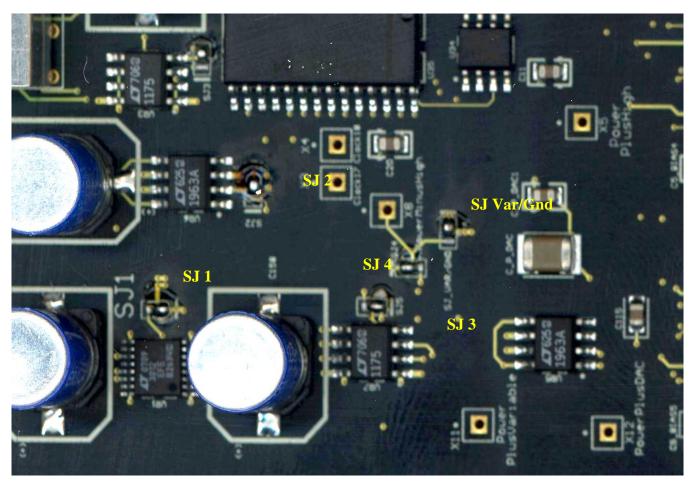

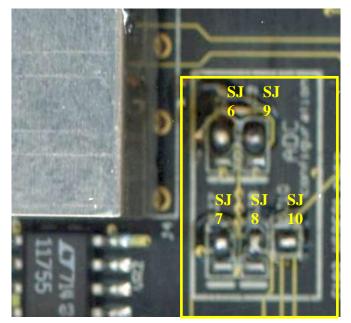

The software reads the ID register, to determine that the correct board is installed in the system. The Board Type tells about what board is installed, Basic Board, AQ32 or other TBD. The Board Sub-type is set by external jumpers to accomplish the different board set-up modes for the specific board (see also Figure 22). The values in ID Register Bit 7..4 determine:

#### Table 16 ID Register Board Sub-Type

| Board Sub-Type              | Set-up                          |

|-----------------------------|---------------------------------|

| Value Bit (74)              | -                               |

| 0                           | Not used                        |

| 1 CCD (Optical) Application | 16 Bit ADC/ 1MHz                |

| Standard Setting            | Clock Low/Hi Range : -10V/ 10V  |

|                             | Bias 1-16 Range : 0V to 28V     |

|                             | Bias 17- 20 Range : 10V to -10V |

| 2 CCD Application           | 16 Bit ADC/ 1MHz                |

|                             | Clock Low/Hi Range : -10V/ 10V  |

|                             | Bias 1-8 Range : 0V to 28V      |

|                             | Bias 9- 16 Range : -5V to 28V   |

|                             | Bias 17- 20 Range : 10V to 10V  |

| 3 CCD Application           | 16 Bit ADC/ 1MHz                |

|                             | Clock Low/Hi Range : -10V/ 10V  |

|                             | Bias 1-8 Range : 0V to 10V      |

|                             | Bias 9- 16 Range : -10V to 10V  |

|                             | Bias 17- 20 Range : -10V to 10V |

| 4                           | 16 Bit ADC/ 1MHz                |

|                             | TBD                             |

| 5 CMOS (IR) Application     | 16 Bit ADC/ 1MHz                |

|                             | Clock Low/Hi Range : -6V / 6V   |

|                             | Bias 1- 8 Range : 0V to 6V      |

|                             | Bias 9-16 Range : 0V to 6V      |

|                             | Bias 17- 20 Range : 0V to 6V    |

| 6,7,8                       | 16 Bit ADC/ 1MHz                |

|                             | TBD                             |

| 9 CCD (Optical) Application | 16 Bit ADC/ 3MHz                |

|                             | Clock Low/Hi Range : -10V/ 10V  |

|                             | Bias 1-16 Range : 0V to 28V     |

## ESO General Detector Controller (NGC) USER MANUAL

| Doc:   | VLT-TRE-ESO-13660-3900 |

|--------|------------------------|

| Issue: | 1.1                    |

| Date:  | 08/03/2006             |

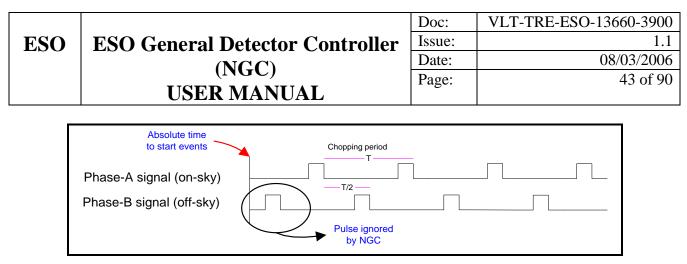

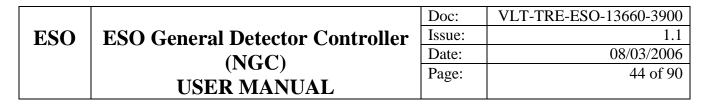

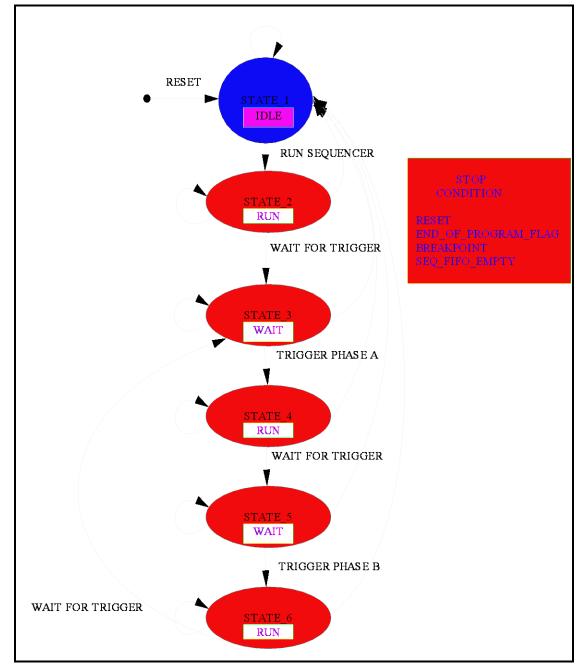

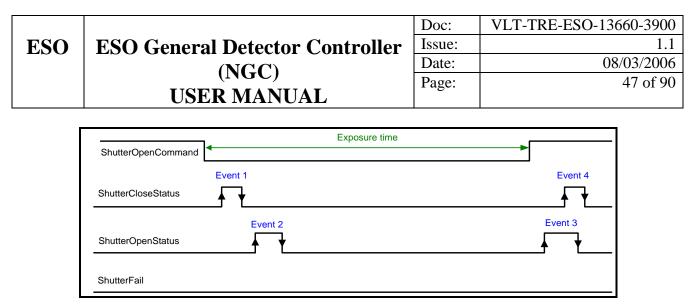

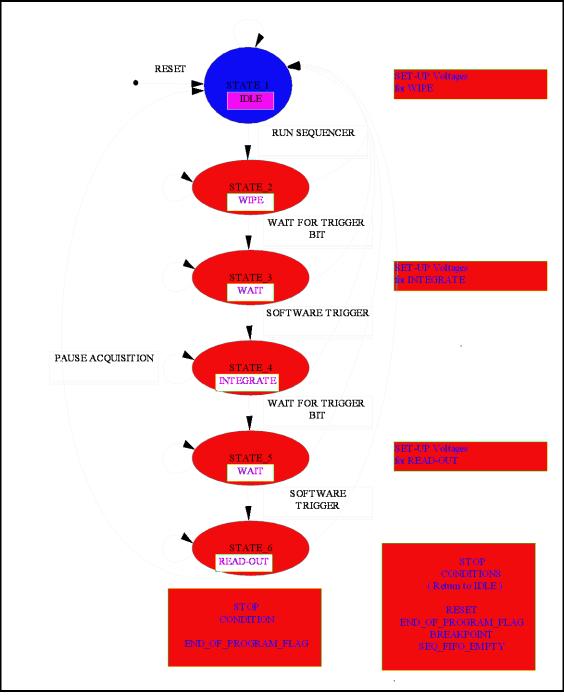

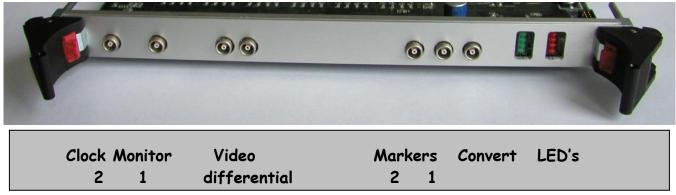

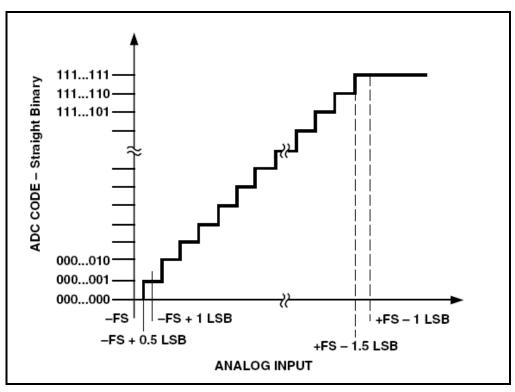

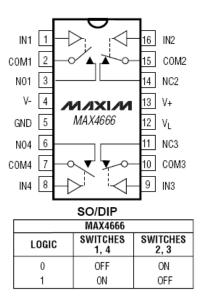

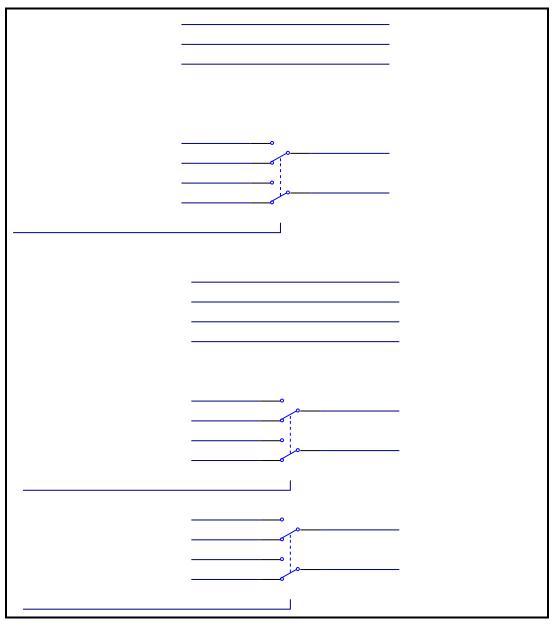

| Page:  | 30 of 90               |